如何對高速通道建模、仿真及眼圖的嵌入和去嵌測試【轉發】

2018-03-29 by:CAE仿真在線 來源:互聯網

信號完整性是分析和緩解高速數字鏈路中噪聲、失真和損耗所帶來的負面影響的系統工程,是高速鏈路性能和系統級可靠性的重要保障。

然而如何保障電氣性能的完整卻是高速電路“攻城獅”的一大難題。熟練的“老鳥”們總能夠應用信號完整性理論,合理地使用仿真和測試工具,快速地解決各種電路的問題。

今天我們就來跟大家聊聊這其中的工具,并提供手把手的視頻讓大家的技術“突飛猛進”。

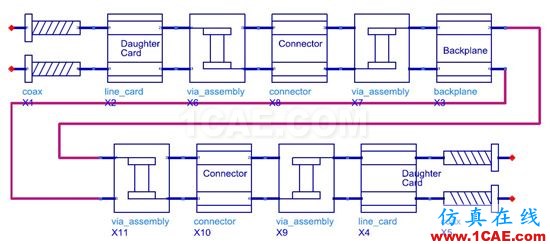

在高速數字信號傳輸中,通道指的是從發射端IO Buffer到接收端IO Buffer之間的電子路徑。它可能由芯片的封裝,PCB板上的走線,連接器和線纜組成。一個簡單的通道可以從發射端IO Buffer,PCB走線到接收端IO Buffer。 一個復雜的通道(例如背板)由圖1所示元件組成。

▲ 圖1. 一個大約20英寸長的通道

在進行通道建模的時候

需要注意三個最重要的特性

1.阻抗;2.損耗;3.延時或者相位

阻抗取決于機械結構,介電常數和金屬導電性。阻抗不匹配將造成多重反射,最終導致信號振鈴、過沖和下沖。

另外通道損耗對SERDES設計很關鍵,信號損失的主要原因是介電損耗和導體損耗,而這些損耗通常是依賴于頻率的。從而一個信道的頻帶寬度限制了其可通過的最大比特率。對于DDR來說,命令、地址和時鐘或DQ和DQS之間的相位差必須被很好的控制。

▲ 圖2. 一個通道中的不同元件

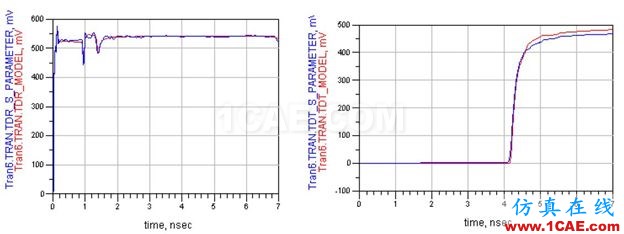

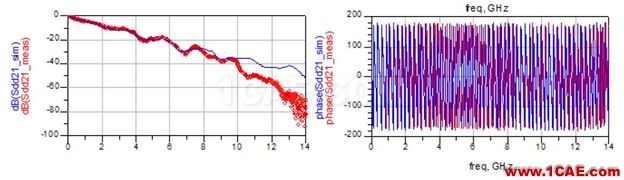

通道的元件可以用基于公式的傳輸線模型、電磁模型或者基于測量的模型建模。對于每個元件的建模正確與否取決于尺寸以及材料參數是否精確。元件模型準確定義好之后,把這些元件級聯起來構建一個完整的通道模型(如圖2所示),就可以通過TDR仿真來估計通道的阻抗和時延(如圖3所示)。通道的插入損耗可以通過S參數仿真估計(如圖4所示)。最終這些仿真結果將為“攻城獅”改善通道性能、支持更高速率傳輸提供調試優化線索。

▲ 圖3.阻抗變化(左)和時延(右)

▲ 圖4. 插入損耗(左)和相位(右)

看到這里小伙伴們基本明白高速通道建模的方法了吧?可是具體怎么來操作呢?下面的視頻將手把手教您“構建具有特定頻率損失的高速通道模型”。

看完小伙伴們是不是對使用ADS構建高速信道模型胸有成竹了呢?通過對信道模型的構建,我可以隨意地調整鏈路參數,來查看這些參數對模型的參數表征的影響,最終找到最優的方案。

在完成了鏈路的仿真優化之后,不可避免的要將優化后的結果應用到具體的電路中,并根據電路的實際情況進行必要的調試,確保產品的實際結果符合預期。這一階段中,Keyisght的示波器就是非常必要的測試工具,能夠輕松、準確地完成對電路信號的各項指標的測試和表征,加快測試驗證的速度。

當然,“老鳥”們往往不滿足于此,更是思考著如何在新板打樣之前能夠“預知”效果,提升優化效率,降低投板次數,縮短產品上市周期。而Keysight示波器可以提供另一款調試“神器”——示波器離線軟件N8900A。

在使用ADS進行鏈路仿真、得到S參數后,可以將模型導入到N8900A中,對高速鏈路前端的實測信號眼圖進行嵌入和去嵌測試,方便“攻城獅”評估高速鏈路模型對真實信號的影響,從而找到調試的線索和方向。

下面的視頻將手把手地教您 “如何使用N8900A Infiniium離線分析軟件對信號進行嵌入和去嵌測試”

這款功能強大又“神奇”的軟件,不單單能夠完成“高速眼圖的嵌入和去嵌測試”它還能夠在“脫離示波器和目標系統”的情況下,打開已保存的波形,并提供與Infiniium示波器一致的界面進行信號的觀察、測試、解碼以及抖動分析功能。

轉自微信公眾號: 信號完整性

相關標簽搜索:如何對高速通道建模、仿真及眼圖的嵌入和去嵌測試【轉發】 HFSS電磁分析培訓 HFSS培訓課程 HFSS技術教程 HFSS無線電仿真 HFSS電磁場仿真 HFSS學習 HFSS視頻教程 天線基礎知識 HFSS代做 天線代做 Fluent、CFX流體分析 HFSS電磁分析