使用Datasheet阻抗進行LDMOS匹配設計

2016-12-27 by:CAE仿真在線 來源:互聯網

引言

本文檔主要介紹了飛思卡爾在處理現今橫向擴散金屬氧化物半導體(LDMOS)器件所采用的阻抗數據表(Datasheet)的方法,其中LDMOS包括單端和推挽兩種結構。此文的目的是闡明器件輸入輸出阻抗匹配網絡數據表的使用。

阻抗提取的方法有多種。本文檔的范圍不包括詳細的提取方法;但介紹了一個可行的提取方法。無論使用哪種方法,主要關心的都是將去嵌入所提取的數據恢復到器件的參考平面的必要性,器件的參考平面如圖1所示。

阻抗的提取需進一步求解MSTEP(Microstrip step in width)器件。是德科技ADS MSTEP仿真元件的用戶展示出了基準平面寬度和銅線焊盤寬度之間的差異。例如圖2就示出了銅引線焊盤寬度(“b”維度)比參考平面寬度(“a”維度)大。

有關此主題的更多信息,本文末尾的參考文獻提供了一個嚴格且精確的阻抗測量方法。

單端器件

圖3為單端器件的阻抗數據表形式。通過調諧夾具以得到器件的最佳性能,然后測得其在參考平面的阻抗,從而生成該器件的阻抗數據表。

圖4表明在使用頻段內器件的阻抗隨頻段變化,數據表形式的阻抗特性可用于優化其性能。

測得的數據可以轉換成S1P文件,如圖5所示。

注意:所測量的阻抗數據的虛部已被共軛化,如圖4所示。

數據表中共軛化后的阻抗可用來計算阻抗的相對旋轉偏移量。這表明,首次測得的阻抗是RF發射點處的視入值。然而,對于S11的優化則需要能夠代表塊的視入阻抗數據。這就是阻抗箭頭重定向和共軛化阻抗數據的原因。

*對于所有主要參數,調諧后的最佳夾具將有總峰值性能;其中主要參數包括:輸入回波損耗(IRL),效率,P1dB,線性,最大輸出功率(Pout)和帶寬。

注意:盡管一些史密斯圓圖由于顯示的原因而使用了不同的歸一化阻抗值,但是在使用本工程公示中的阻抗數據時,設計師們應假定阻抗是基于50Ω系統。

圖6中的通用匹配電路將用于優化初步設計中的匹配網絡。

圖5中的MRF19125阻抗數據是作為建立初步設計匹配網絡的一個實際例子,匹配網絡如圖8所示。其中一些關鍵的細節如下:

?該S1P文件被用作一個雙端口(基準為接地端口)器件并作為文件名的格式。

?該直流塊和旁路電容只顯示通用值。

?在理想情況下,從直流電源饋電到 DUT交界處的微帶線應該有λ/ 4長。

?簡化的C_BYPASS電容應盡可能的離微帶線條近。

注:這里給出的是一個簡單的匹配網絡,它也可能被拓展成一個任何其他結構的拓撲電路。

前面已經討論過的MSTEP必元件須放置在器件與第一匹配元件MLIN(放置位置的細節見圖6,8,10和11)之間。MSTEP塊極其重要,因為它被用于確定參考平面的寬度和銅引線焊盤寬度之間的差異。如果這些值不相同,阻抗將會不連續。MSTEP由其寬度值(“a”和“b”)確定。對于尺寸“a”的值,可以參照封裝尺寸數據表。尺寸“b”是引腳將要焊接在PCB板上的銅焊盤長度。

MTEE(Libra Microstrip T-Junction)是ADS的另一仿真元件,它用于連接的偏置饋給(參見圖7)。該MTEE設計了違背典型的優化夾具布局的規則。一個簡單的節點連接已足夠準確地模擬阻抗。然而,如果可能的話,在它的使用限制范圍內仍建議采用MTEE。

現在,阻抗數據已獲得,共軛化后重新插入在了一個*.s1p文件里。下一步就是使用SP1塊來優化仿真S參數,如圖8所示。匹配網絡S11應調諧到至少-30 dB(或盡可能低),則第一個輸入匹配電路就完成了。重復這一過程,利用輸出阻抗來完成輸出匹配,。最后,該匹配網絡將在印制電路板PCB上實現。

推挽式器件

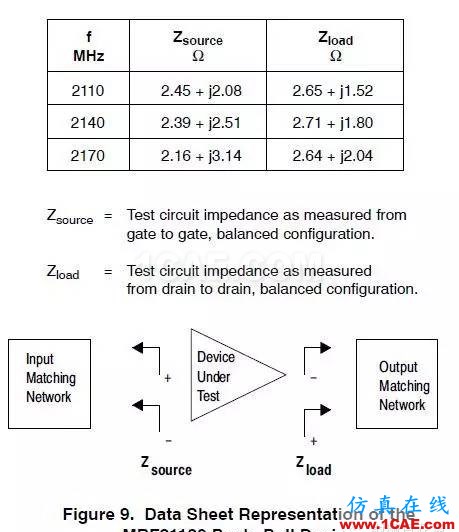

推挽式器件獲取阻抗的方法與單端器件從固定夾具上獲取阻抗的方法類似.其具有代表性的阻抗值如圖9所示.

推挽式器件阻抗數據應在數據存儲裝置中顯示出來,圖10展示了一個范例。

注意:圖9中的測量阻抗數據的虛部已被共軛化,這與單端器件的處理方法相同。

用于初步設計優化推挽式器件輸入和輸出端匹配網絡的方法和單端器件的相同。

圖11示出了用于初步設計優化輸入匹配網絡的電路。圖11所示的平衡-不平衡巴倫是一種理想化的三端口器件,通常其輸入/輸出的阻抗比為n:1。

圖12展示了主要模塊:

?通用匹配網絡

?直流電源饋電塊1和2

?MSTEP塊

?用戶定義的三端口子電路(巴倫)

?兩端口*.s1p

在一個好的初步設計中,圖12所示的通用匹配網絡代表了典型可實現的電路元器件組。網絡的拓撲結構不限于圖12所示的這一種。這個拓撲結構只是一個典型的設計。

這兩個直流饋電塊和MSTEP塊與圖7 單端器件的類似,它們有著相同的功能。

圖12中的這個三端口子電路可以是ADS里(用戶可以設計)的巴倫,或者是由Sonnet 或一款類似電磁仿真仿真軟件生成的*.s3p文件。

兩端口的S1P數據塊文件代表了MRF21180共軛化后的阻抗數據。這個塊有兩個端口代表了共軛化后的阻抗,另外第三個端口是參考地。

結論

這個工程公示文檔給出了一個關于怎樣基于實測阻抗數據完成匹配結構的簡明方法。盡管還有其他的解決辦法,但使用這個方法可以為設計師的最終設計提供一個好的近似值。

引用文獻

J.J.Bouny, “Impedance Measurements for High Power RF Transistors Using the TRLMethod,” MicrowaveJournal, October 1999。

原文作者:Darin Wagner ,Freescale

相關標簽搜索:使用Datasheet阻抗進行LDMOS匹配設計 HFSS電磁分析培訓 HFSS培訓課程 HFSS技術教程 HFSS無線電仿真 HFSS電磁場仿真 HFSS學習 HFSS視頻教程 天線基礎知識 HFSS代做 天線代做 Fluent、CFX流體分析 HFSS電磁分析