信號完整性SI(SignalIntergrity)概述之一高速串行信號的仿真

2016-10-12 by:CAE仿真在線 來源:互聯網

隨著系統速率的逐年提升,高速數字信號的速率越來越高,信號完整性SI(Signal Integrity)越來越受到關注。信號完整性(Signal Integrity)簡稱SI,是指在信號線上的信號質量,數字信號質量差,不是由某一單一的因素導致的,而是PCB設計中多種共同的因素共同引起的,如器件選型,PCB板阻抗,損耗控制,模數混合設計等,主要表現的信號完整性問題包括反射,串擾,地彈,振鈴等。

特別是興森科技有些客戶經常反饋的,較大的過沖,振鈴,加上系統較小的噪聲裕量,給系統時鐘帶來了非單調性,造成系統的誤判,這是令所有硬件開發人員頭疼的事情,有時候即使通過高速實驗室調試,測試的方法找到了問題的原因,但是PCB已經成型,不得不再次花大把的時間跟金錢重新打板,貼裝,調試,據興森科技現有設計類客戶統計平均改板次數為1.2次。

所以通過在研發階段借助目前的EDA仿真工具,將SI問題定位在設計的前端尤為重要。客戶的問題就是興森科技的問題,在這里將分期為大家介紹高速系統中的信號完整性問題。

(1)高速串行信號完整性分析

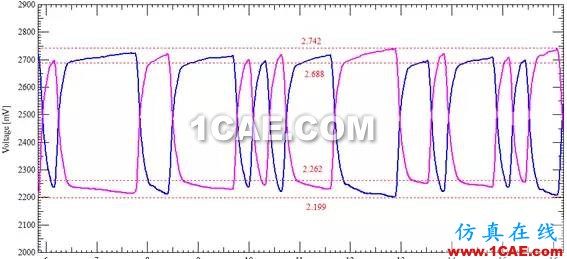

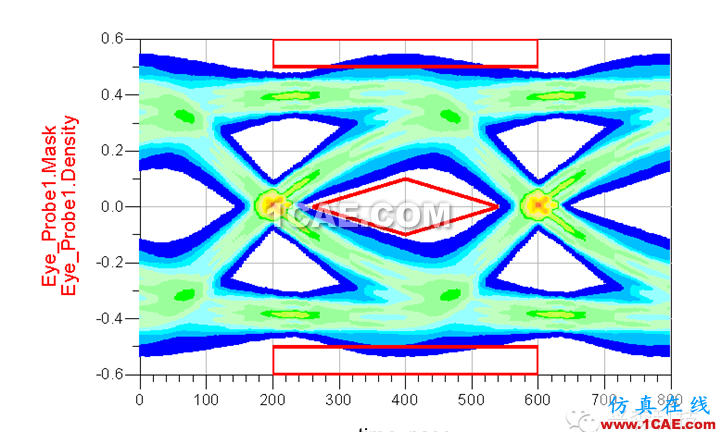

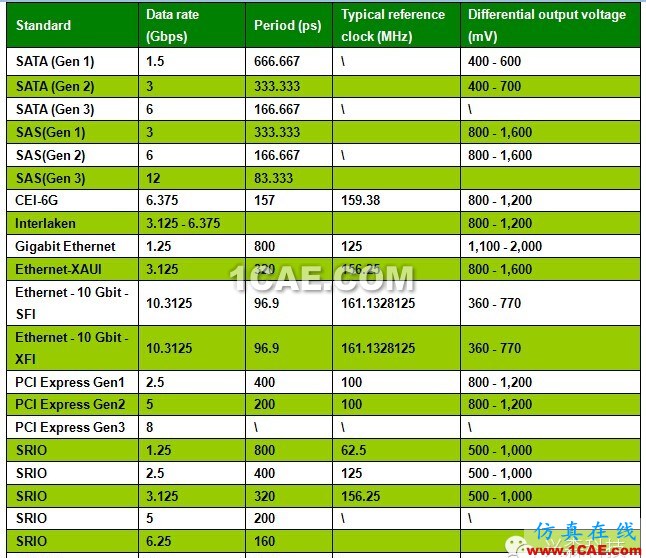

常見的高速信號如PCIE,SATA,GTX,GTP,SRIO,USB3.0,XFP,SFP,XAUI等,評估整條鏈路上信號從發射端到接收端的表現情況,通過頻域上(如S參數)和時域上(如信號波形,眼圖)的仿真評估,來確保信號的有效傳輸。

圖一:常見的串行背板

圖二:高速信號波形圖

表一:常見的高速信號列表

(2)高速背板信號完整性分析

通過背板的仿真,可以有效地解決高速信號經過較長背板后由于衰減及反射等信號完整性問題而引起的信號不能有效地進行傳輸的問題,背板的仿真可以指導客戶選擇適當的背板材料,并對高速連接器進行優化,有效的降低研發成本,減短設計周期。

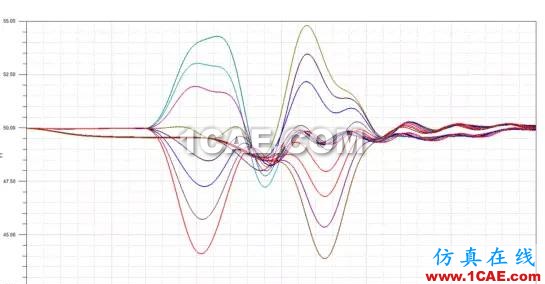

圖四:不同層信號的損耗

(3)過孔優化

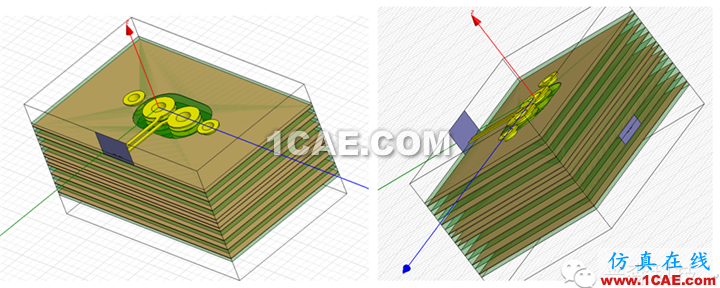

對于PCB上高速的換層過孔和連接器過孔,通過3D軟件建模分析,有效地控制過孔阻抗,給出過孔的最優尺寸,從而優化信號質量,提高設計成功率。

圖五: 過孔3D模型

圖六:不同反焊盤對過孔阻抗的影響

綜上所述:

整個高速串行通道中,PCB設計的線寬線距,過孔的物理結構,走線的層次選擇,是否背鉆(back drill)都會影響到高速數字信號的傳輸,都需要前期仿真介入,做到科學設計,無憂無慮。

相關標簽搜索:信號完整性SI(SignalIntergrity)概述之一高速串行信號的仿真 HFSS電磁分析培訓 HFSS培訓課程 HFSS技術教程 HFSS無線電仿真 HFSS電磁場仿真 HFSS學習 HFSS視頻教程 天線基礎知識 HFSS代做 天線代做 Fluent、CFX流體分析 HFSS電磁分析